~DATE: Harch 29, 1976

PE-T-232

Programming and Engineering Staff

FROM: M. L. Grubin

SUBJECT: P-4CC PROCESS EXCHANGE AND NEW PROTOCOLS

I. Frocess Exchange

- A. Data Bases

1. Ready List

2. WAIT Lists

3. Process Control Block (PCB)

- E. Instruction Primitives

1. WAIT

2. NOTIFY

- C. Dispatcher and Register File Management

1. Ready List Maintenance

2. Register Set Assignment

3. Fetch Cycle Trap

II. Traps, Interrupts, Faults, Checks

- A. External Interrupts

1. Operation

2. Special Instructions (IRTN, INOTIFY)

- E. Faults 1. Cata Bases 2. CALF 3. Fault Handler

- C. Checks

- III. Register Files

- IV. Control Panel

- V. CP Timer

2

PE-T-232

-knodeloodilaan 1999 - Hook Idatu ahaan soori

57 INFOR 14 2 1

36.2

huonsil : PROCESS EXCHANGE

Digos (2) years Digos (2) years Digos The Process Exchange mechanism is composed of three data bases and two Joy basic instruction primitives. The data bases are the ready list, wait lists, and Process Control Blocks (PCB). The basic instruction primitives are WAIT and NOTIFY. In addition, there is an independent mechanism for controlling the usage of two register sets which is prelated to, but not part of, the ready list data base.

A. Data Bases

1. Ready List

The ready list is a two-dimensional list structure used for priority scheduling and dispatching of processes. The entire ready list data base (excluding live registers) and all PCB's are contained in a "single segment. The segment number of this segment is contained in a 16-bit register called OWNERH. Within the segment, all pointers and site accresses (except fault vectors and wait list pointers) are 16-bit word number quantities.

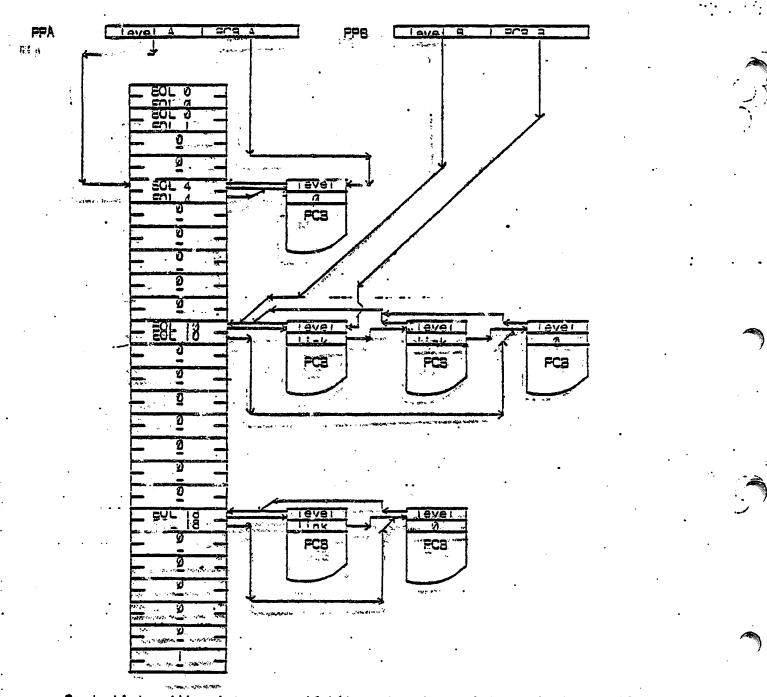

The two-dimensionality of the ready list is achieved with a linear array of list headers for each priority level composed of a Seginning of List (201) pointer and an End of List (201) pointer.

Each pointer is the 16-bit word number address of a PCB (in the same segment as the ready list). The PCB's on each priority level list are forward-threaded through a 16-bit link word, and as many PCB's as desired can be threaded together on each priority level to form the ready list. A process' priority level is both determined by and encoded as the address of a BOL pointer in the ready list. Priority order is determined by arithmetic comparison, i.e., smaller numbers (addresses) are higher priorities. As a result, priority level list headers must be allocated in contiguous memory at system startup time.

The end of the ready list is determined by a BOL containing a 1 (PCB addresses must be even). An empty level is indicated by a 20L containing 0. Figure 1 is a picture of the ready list structure. The 32-bit registers PFA (Pointer to Process A) and PPB (Pointer to Process S) are a speed-up mechanism for locating the next process to PPA always contains both the level (BOL pointer) and PCB cispatch\_ accress (designated level A and PCBA) of the currently active process. -Pfä points to the NEXT process to be run when process A 'goes away'. PPA not only points to the currently active process, but, by definition, level A is the highest level in the system. It is possible for PPE and PPA to be 'invalid'. This condition is indicated by a PCB address of C. It is important NOT to disturb the level portions, especially level A since, even if invalid, level A indicates the highest level that WAS in the system and therefore determines where in the ready list to begin a scan, if necessary (PPB, invalid), for th next process to run. In a completely idle system, both PPA and PPE 🦡 will be invalid and, upon completion of the ready list scan, the u-code .will go into a 'wait for interrupt' loop.

It is important to notice that there is no word number pointer to the first priority level in the ready list. The ready list allocator, ch starts the process exchange mechanism, knows where the list egins and, during execution, level A (in PPA) will always point to either the highest level currently in the system or the last. known highest level and, hence, acts as an effective ready list begin cointer. In addition, level B will always be higher than the fisecond level to run. That is, a PCB can never be on a level higher than level B unless it is the only PCB higher than level B (i.e., level A)

.

5 . Q . . K

Two "queuing" algorithms will be implemented for the ready list, either FIFO or LIFO queuing.

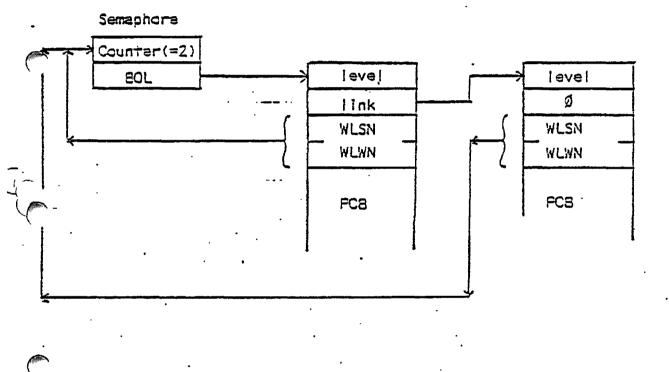

2. WAIT Lists

Every PCE in the system will always be somewhere. If it is not on the ready list, then, by definition, it will be on a wait list. A wait fist is defined by a 32-bit semaphore consisting of a 16-bit counter () and a 16-bit word number SOL pointer. Since the ready list and all PCE's reside in one segment (OWNERH), and only PCE's go onto wait lists, a segment number is not needed in the semaphore. However, semaphores themselves can be anywhere and, in general, are NOT in the FCE segment. The structure of a wait list is shown in figure 2. "Notice that the last block on the wait list contains a G link word. "tice also that the semaphore contains only a BOL pointer.

("ne 'queuing' algorithm for wait lists is process priority queuing. That is, the priority level of a PCE will determine where on the wait list the PCB will be queued. For PCE's of equal priority, the algorithm becomes FIFO.

3. Process Control Block (PCB)

The contents of the PCE are shown in Figure 3. The PCE can be broken (ito the following logical sections which are ordered as shown:

a. Control

0 - Level (pointer to 60L in ready list)

1 - Link (pointer to next PCB or 0)

2.3 - SN/AN of Wait List this block is currently on (SN=0 indicates on ready list)

. . . . . . . . . . . .

4 - abort flags used to generate Process Fault when PCB is dispatched.

Current bit assignments 1-15: MEZ 16: process interval

timer overflou

S.7 - reserved

b. Process State

8,9 - Process elapsed timers (must be maintained by software that resets the interval timer)

| an a        |                                                                                                                                                                                                                                                                  | د ، ورانگناند، ، ویکیکیون د .<br>او از بورانگناند، ، ویکیکیون د |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| ·<br>·                                          |                                                                                                                                                                                                                                                                  | • • •                                                           |

|                                                 |                                                                                                                                                                                                                                                                  |                                                                 |

| ※登録部の はかのです。<br>の登録の いたするため。                    | Page 4                                                                                                                                                                                                                                                           | PE-T-232                                                        |

| nogi stylet                                     |                                                                                                                                                                                                                                                                  | . A                                                             |

| . జ∼ురిజ<br>తిరిహద్య సం                         | 19-13 - DTAR2 and DTAR3 (never saved, always restor<br>14 - Process Interval Timer with 1.024 msec reso                                                                                                                                                          |                                                                 |

|                                                 | 15 - Reserved                                                                                                                                                                                                                                                    |                                                                 |

| •                                               | 16 - Save mask - used to avoid saving and registers = 0                                                                                                                                                                                                          | restoring                                                       |

|                                                 | Bits 1-8: GRC-GR7 (2 words each)                                                                                                                                                                                                                                 |                                                                 |

|                                                 | 9-12: FPC-FP1 (4 registers, 2<br>13-16: Base Registers(PR,SB,LE,                                                                                                                                                                                                 |                                                                 |

| 2. <del>2</del> <b>1</b>                        | 17 - Keys                                                                                                                                                                                                                                                        |                                                                 |

| · · · · ·                                       | 18,33 - GRÙ-GR7<br>34,41 - FPO-FF1                                                                                                                                                                                                                               |                                                                 |

|                                                 | 42,49 - Base Registers (PE,SE,LB,XB)                                                                                                                                                                                                                             | •                                                               |

|                                                 | Note that although all the registers are assigned                                                                                                                                                                                                                | locations                                                       |

|                                                 | within the PCE, only non-zero registers will actual                                                                                                                                                                                                              | Ly be saved                                                     |

|                                                 | which results in a compacted list which can only be<br>by the bits in the save mask. In general, the save                                                                                                                                                        |                                                                 |

|                                                 | (those not equal to 0) will be between words 18 a                                                                                                                                                                                                                | nd 49. The '                                                    |

| · (                                             | order of the registers, however, is fixed as above.                                                                                                                                                                                                              | •                                                               |

|                                                 | Fault (See section on Faults for a description of t<br>this portion of the PCB)                                                                                                                                                                                  | he use of                                                       |

|                                                 | 50,59 - Fault Vectors: SN/4N pointers to fault<br>Ring C, Ring 1, Page Fault<br>fault handlers                                                                                                                                                                   |                                                                 |

|                                                 | 60,62 - Concealed Fault Stack Header                                                                                                                                                                                                                             | •                                                               |

| . · · ·                                         | 63 Concealed Stack - 6 word entries. (This<br>not start at word 63).                                                                                                                                                                                             | stack need                                                      |

| · 8. Instr                                      | uction Primitives                                                                                                                                                                                                                                                |                                                                 |

| mechanism<br>These ins<br>essential<br>(42-tit) | two basic instruction primitives for the proces<br>NOTIFY and WAIT. In addition, NOTIFY has tw<br>tructions, similar to Djikstra's P and V oper<br>ly "interlock" mechanisms. These instructions are<br>"instructions" as follows:                               | o variants.<br>ators, are                                       |

|                                                 | Instruction (16-bit universal generic)<br>32-bit pointer to semaphore address                                                                                                                                                                                    |                                                                 |

| unit reco<br>that an                            | ted by the names, WAIT is used to wait for an event<br>rd device available, whatever) and MOTIFY is used<br>event has occurred. In particular, a WAIT is used<br>and a NOTIFY is used to alert a process which is wa                                             | to signal<br>to wait for                                        |

| and a B<br>of that s<br>0, indica               | ion is achieved by means of a semaphore containing<br>OL pointer. The semaphore and the PCB's waiting for<br>emaphore constitute a wait list. The counter, if g<br>tes the number of PCE's on the wait list. If ne<br>the number of processes that can obtain th | r the event<br>reater than<br>cative, it                        |

| Semaphore                                       | the number of processes that can obtain th<br>s fall into two categories: public and private.<br>is used to ccordinate several processes together of                                                                                                             | A public                                                        |

| semaphore<br>System r                           | is used to coordinate several processes together o<br>esource. Frivate semaphores are used by a single                                                                                                                                                           | e process to 🖉                                                  |

| :                                               |                                                                                                                                                                                                                                                                  |                                                                 |

| · · · · · · ·                                   |                                                                                                                                                                                                                                                                  | en e                        |

|                                                 |                                                                                                                                                                                                                                                                  |                                                                 |

٠,

•

.

Page 5 ...

coordinate its own activities. For example, if a cisk reduest is made, recess will wait on a private semaphore for the disk operation to aplete. The disk process will then notify the semaphore upon completion. The distinguishing characteristics of a private semaphore is that only 1 PCB can ever be on that wait list. A public semaphore can have many different PCE's on its wait list.

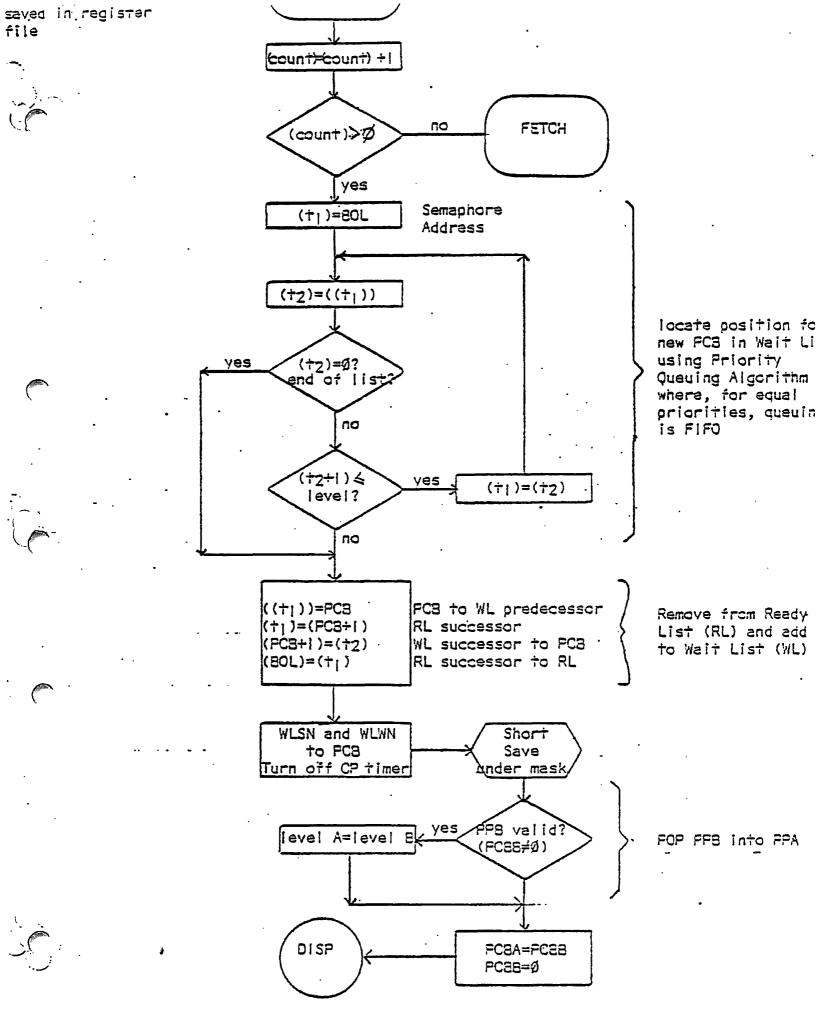

## 1. WAIT

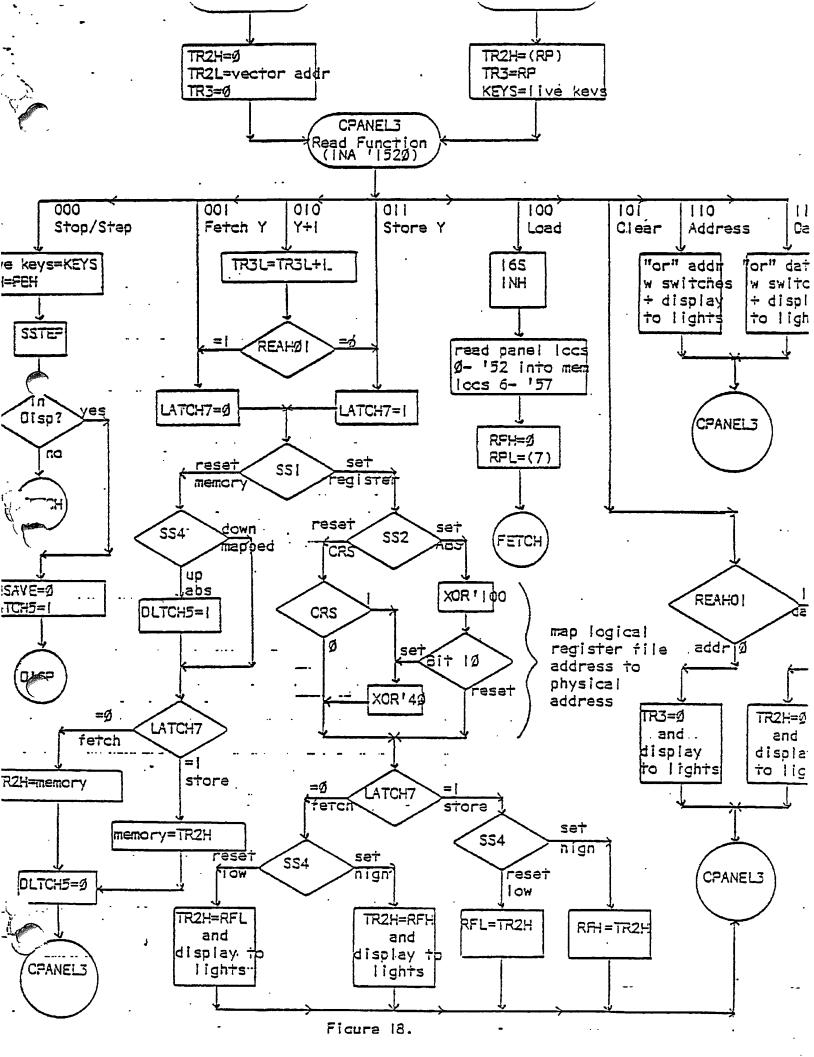

The operation of wait is as follows: the semaphore counter is incremented and, if greater than 0, (resource not available/event has not occurred), the PCB is removed from the ready list and added to the specified wait list. If the counter is less than or equal to 0, the process continues. If the PCB is put on the wait list, the general registers are NOT saved and the register set is made available. Therefore, a process can NEVER depend on the general registers being intact after a WAIT. In fact, from the point of view of an executing occess, a WAIT appears as a NOP which destroys the registers. In accition, WAIT will turn off the process timer. Figure 4 is a detailed flow chart of the WAIT instruction.

2. NOTIFY

-----

NGTIFY instruction has two flavors:

NFYE: use FIFO queuing op code Bit 16 = 0NFYE: use LIFO queuing op code Bit 16 = 1

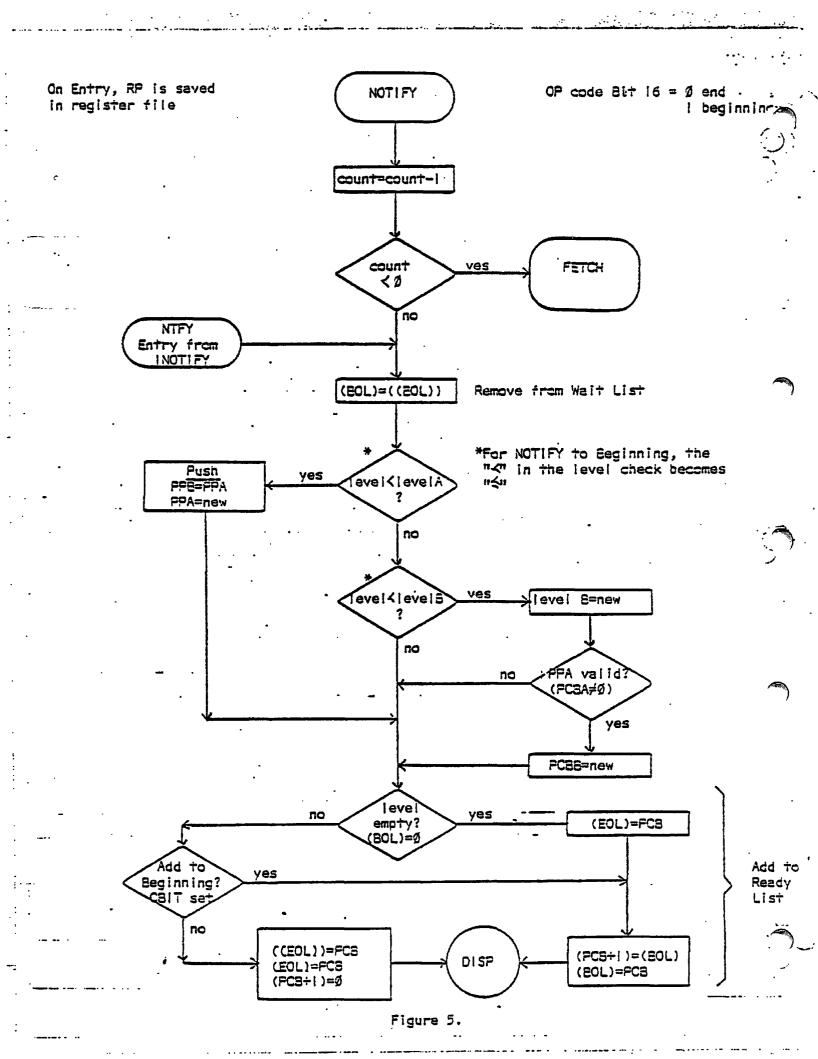

The instructions differ GNLY in the ready list queuing algorithm used. The operation of NOTIFY is as follows: the semaphore counter is decremented and the notifying process continues. If the counter is less than 0, no action is taken, but if greater than or equal to 0, a PCE is removed from the top of the wait list and added to the ready wist. No explicit action is ever taken on the notifying process, only lie notified semaphore. If a notified process is of higher priority than the notifying process, the latter will be effectively "interrupted", but will remain on the ready list. Figure 5 is a detailed flow chart of the NOTIFY instruction.

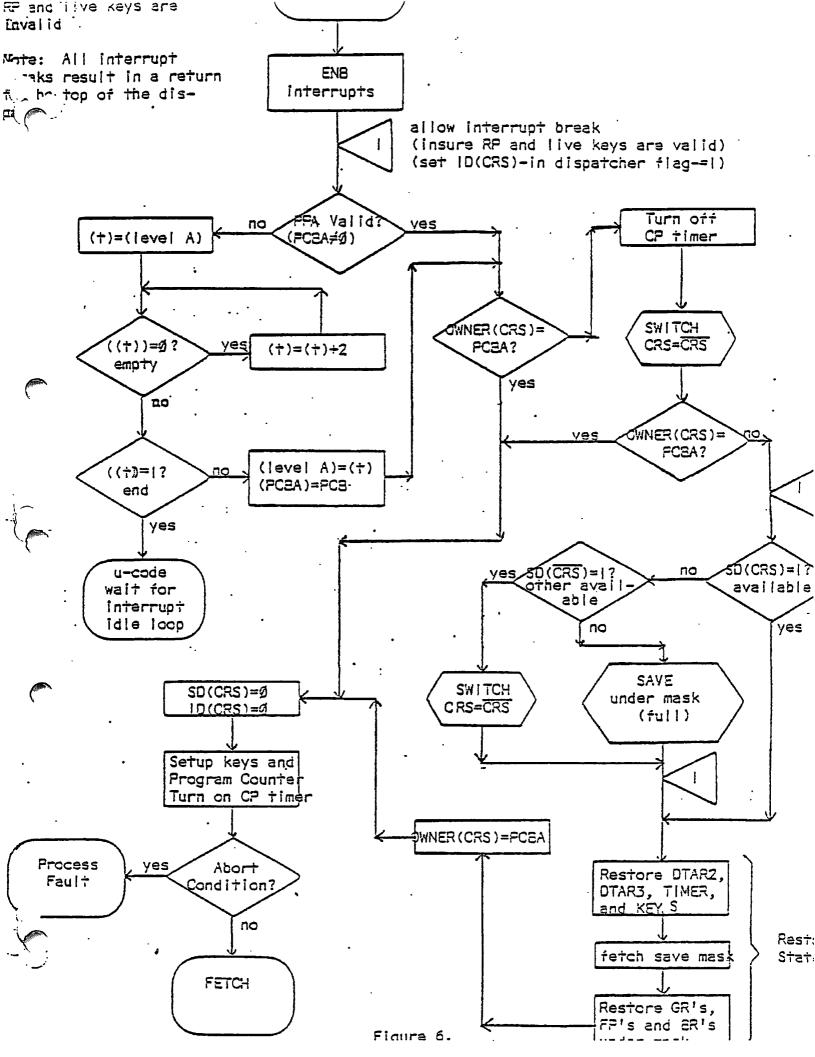

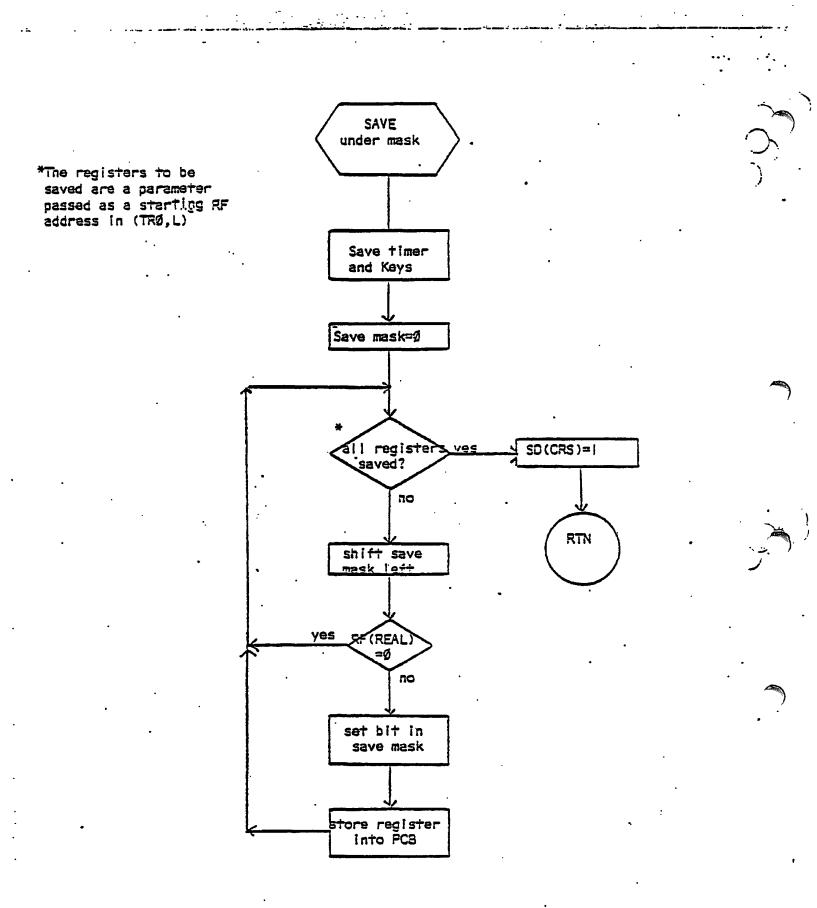

C. Dispatcher and Register File Management

The dispatcher is the root of the process exchange mechanism and is responsible for determining the next process to run (be dispatched), and assigning that process a register set. There is considerable overlap with NOTIFY and WAIT in functionality related to maintaining the ready list. For example, both NOTIFY and WAIT update PPA and PPB as appropriate, but the dispatcher scans the ready list if PPA is ralic. Register file management, including any necessary saves and estores, are the sole province of the dispatcher. Figures 6 and 7 are detailed flow charts of the dispatcher.

# 1. Ready List Maintenance

\* \* \* \* \*

5

Upon entry, the dispatcher first asks if PPA is valid. If it is, the process is assigned a register set and dispatched. If PPA is not valid, a scan of the ready list is initiated. If a PCP is found, PPA is adjusted and the process dispatched. If the ready list is empty, the dispatcher idles. Whenever a process is dispatched the process g timer is turned on.

## 2. Register Set Assignment

In each register set, a register, designated CWNER, contains a pointer to the PCB of the process which owns the set. OWNER is a full 32-bit pointer and OwNERH is used throughout the system to determine the segment number of the ready list and PCE's. Obviously, OWNERH must be the same in both register sets. In addition, the low order bit of the keys register (KEYSH) is used to indicate whether the register set is available. The bit is called the Save Done bit and, if set, indicates that the register set and its copy in the owner's PCB are identical (a save has been done). This bit is set by the save routine (called from wAIT or the dispatcher) and reset when a process is dispatched. Whether a register set is available (SD=1) or not, it is always owned. Therefore, if a process goes away (either as a result of a WAIT or the notification of a higher level process) and comes back agai immediately and, if that process still owns the register set, a restore operation is not necessary. If a register set switch is necessary, the process timer is turned off. The details of selecting which register set to assign to a process being dispatched is shown on the right of Figure 6. The dispatcher is the only code which switches register sets.

#### 3. Fetch Cycle Trap

At various points in the dispatcher (indicated by I on the flow chart) a check for interrupt pending (fetch cycle trap) is made. As a result, interrupts can occur either in the fetch cycle or in the dispatcher. The possible Fetch Cycle traps are:

- 1. External Interrupt (See Part II-A)

- CP-timer increment and possible overflow (See Part V)

.....

- 3. Power Failure (See Part II-C)

- 4. Halt switch on control panel (See Part IV)

- End-of-Instruction Trap 5.

The end-of-instruction trap occurs either from an ECC corrected error or from a missing memory module, memory parity, or machine check during 1/0. In all cases, if the check handling software returns (via LPSW instruction), the possible destinations are either the fetch cycle o the dispatcher (FB in PSM not a real program counter). In order to " cuarantee the proper destination, bit 15 of the keys (KEYSH) — is used  $\mathbb{L}^3$ to incicate if the trap was detected by the dispatcher (bit 15=1).

and the state of the second second

PE-T-232

$\left\{ \mathcal{P} \right\}$

Page /

This bit is set by the dispatcher upon detecting a trap and is reset

I'L. TRAPS, INTERRUPTS, FAULTS, CHECKS

Four words used frequently are 'trap', 'interrupt' (or 'external interrupt'), 'fault', and 'check'. The meanings of these terms are carefully distinguished for the P-400/500. Software breaks in execution are divided into three main categories referred to as 'interrupts', 'faults', and 'checks'. The word 'trap', on the other hand, refers to a break in execution flow on the u-code level.

Traps can occur for many reasons, not all of which cause software visible action, and are always processed on the u-code level. Some traps may directly or indirectly cause breaks in software execution, but not all software breaks are the result of a trap.

On the PRIME 3CO, interrupts, faults, and checks used the same protocol get to their respective software handlers, namely they caused a vector through a dedicated sector 0 location (JST\* vector). On the P-40C/500, when process exchange mode is enabled, the three categories use different protocols both from the P-300 and each other. Roughly, the three terms are used to describe:

- 1. Interrupt a signal has been received from a device in the external world (including clocks) indicating that the device either needs to be serviced or has completed an operation. In general, an interrupt is not the result of an operation initiated by the currently executing software and will not be processed by that software (though, of course, it may).

- 2. fault a condition has been detected that requires software intervention as a direct result of the currently executing software. In general, faults can be handled by the current software, though in many cases common supervisor code within the current process handles the fault. Also, in general, an external device in the real world is not directly involved in either the cause or cure of a fault condition. Often, however, external devices are involved indirectly as, for example, in performing a page turn operation as a result of a page fault.

3. Check

4

- an internal CP consistency problem has been detected which requires software intervention. The condition could be either an integrity violation, reference to a memory module which does not exist, or a power failure. By contrast, a reference to a page which is not resident or an arithmetic operation which causes an exception is a FAULT condition.

#### A. External Interrupts

# 1. Cperation

. .

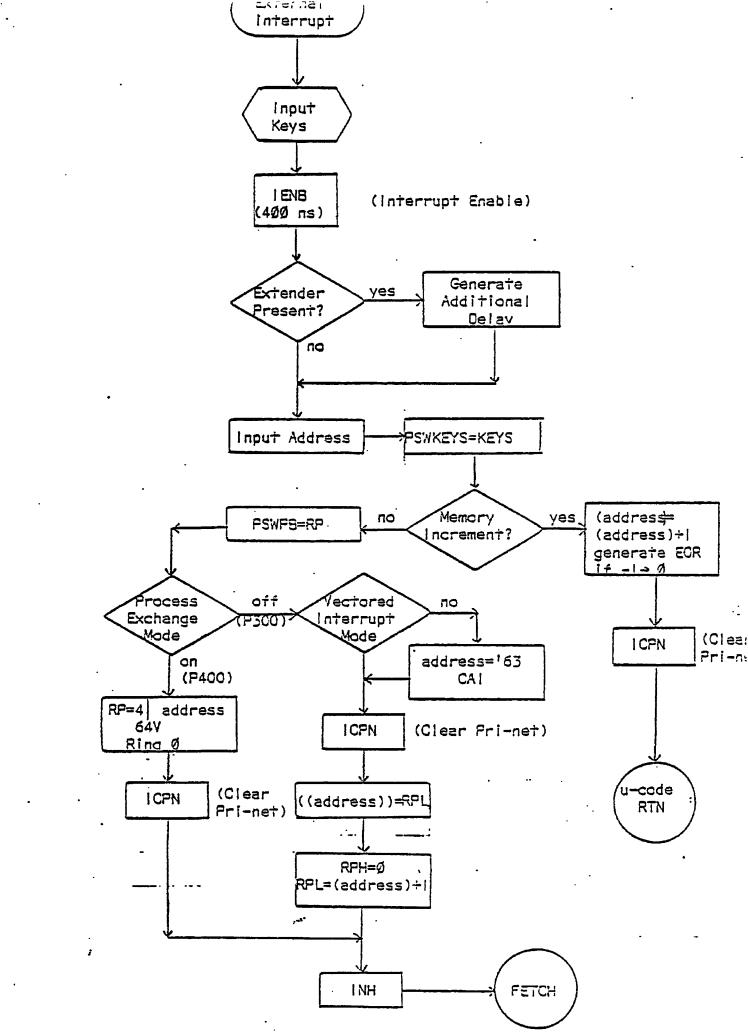

External Interrupts operate in either of two modes depending upon whether process exchange is turned on. If process exchange is off, all interrupts are treated as F-300 interrupts. In all cases, except memory increment, the address presented by the controller (or \*63 if in standard interrupt mode) is used as the address in segment 0 of a 16-bit vector. This vector, in turn, points to interrupt response code (IRC), also in segment 0, which is entered via a simulated JST\* through the vector. Thus, the current P-counter (RPL) is stored in (vector) and execution begins at location (vector) +1 with interrupts inhibited, but with no other keys or modals changed. If in vectored interrupt mode, it is the responsibility of the software to do a CAI. In either mode, the full RP is saved in the register PSWPE.

If process exchange mode is on, an entirely different mechanism operates. In all cases, except memory increment, the address presented by the controller is used as a 16-bit word number offset into the interrupt segment (#4). This segment is guaranteed to be in memory, but STLE misses may occur. The current PB (actually RP) and KEYS (keys and modals) are saved in the u-code scratch registers PSWPB and PSWKEYS. The machine is then inhibited and the IRC begins execution i. 64V mace. It is the responsibility of the IRC to issue a CAI. It isimportant to note that the IRC in the interrupt segment does not belong to any process. PFA points to the PCB of the interrupted process and, in fact, no PCB exists for the IRC. Also, except for PB and KEYS, no registers are saved. In fact, even PSWPB and PSWKEYS are in the register file and not in memory. As a result, the IRC cannot do an enable and must return to the process exchange mechanism (i.e., the dispatcher) as soon as possible. Because of all these restrictions on what the immediate IRC can do, as well as the fact that it does not belong to any process, it is referred to as phantom interrupt code. Unless the job of servicing an interrupt is very simple, phantom interrupt code can do little more than turn off the controller's interrupt mask, issue a CAI, and NOTIFY the real IRC.

A memory increment interrupt is handled the same regardless of the state of process exchange. The address presented by the controller is used as the 16-bit word number in segment 0 (I/O segment) of a 16-bit memory cell to be incremented. If the counter does not overflow (-1->0), the u-code simply returns. With process exchange off, the return is always to the fetch cycle. With process exchange on, the return is either to the fetch cycle or the dispatcher, depending upon where the interrupt was detected. When detecting an interrupt, the dispatcher always insures that RP=F8 and that all live keys=K2YS. If memory increment returns, it does so to the top of the dispatcher without having touched PE or KEYS. In this way, memory increment i quaranteed not to destroy any vital information needed by the dispatcher. If the memory cell counter does overflow, an End-of-Range interrupt is generated and then memory increment returns. The

Page

8

PE-T-232

Esequent EOR interrupt will then be treated like any other external it rupt. Figure 8 is a detailed flow chart of the external interrupt ler.

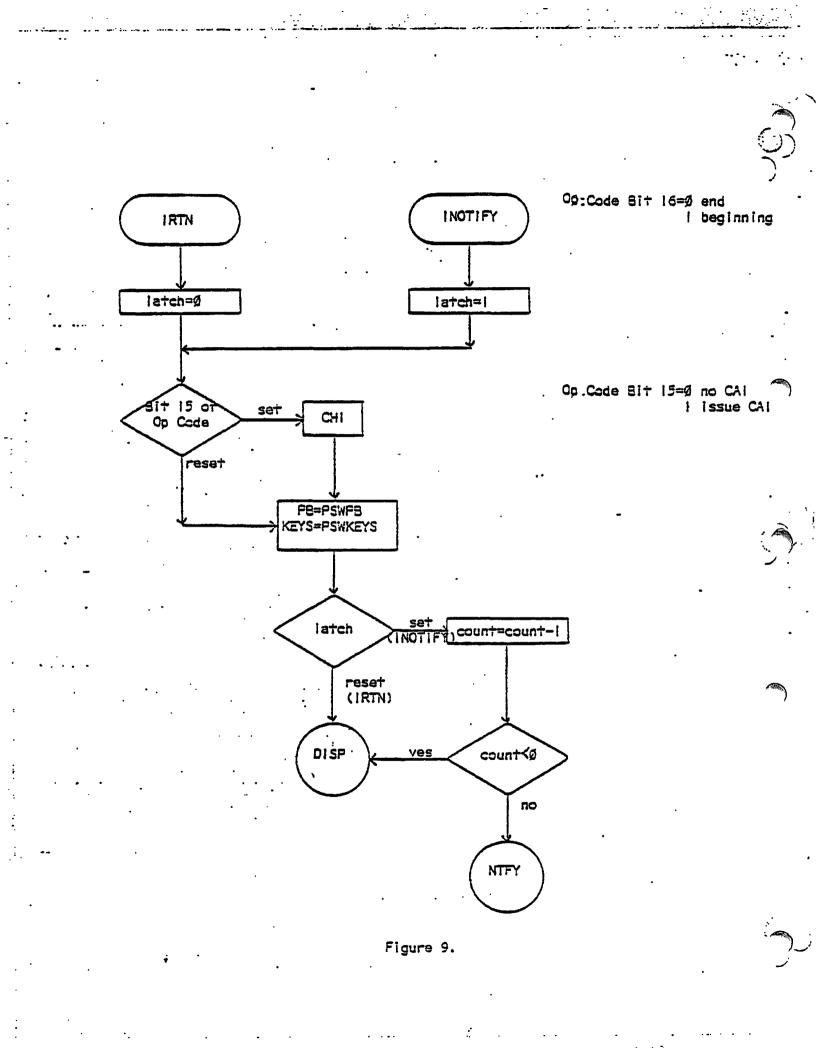

# Z. Special Instructions (IRTN, INOTIFY)

Phantom interrupt code has two options for the actions it can take. If the servicing required by the interrupt is very simple, phantom code can completely process the interrupt and return to the dispatcher. If the servicing required is more complex, the phantom code must turn off the controller's interrupt mask and NOTIFY the remainder of the IRC. In the first case, PB and KEYS must be restored from PSWPB and PSWKEYS and then the dispatcher must be entered directly. Since PB cannot be restored in phantom code (the F-counter will point to the instruction im phantom code) and the dispatcher cannot be entered directly (no such instruction exists), the special instruction, IRTN, a 16-bit generic, is executed to perform these functions. After entering the d. patcher via an IRTN, the dispatcher does not know that an interrupt accurred.

In order to NOTIFY a process, phantom code must insure that FB and KEYS are restored before issuing the NOTIFY. The special instruction, INUTIFY, performs the restore and then does the NOTIFY. As NOTIFY, -WTIFY is a three-word generic with two flavors, INOTIFYB and INOTIFYE e the beginning of list option has bit 16=1 and the end of list ion has bit 16=C in the opcode.

Phantom Interrupt code can issue a CAI in one of two ways. Either an explicit CAI instruction may be issued or the IRTN/INOTIFY instructions can issue it. Bit 15 of the IRTN/INOTIFY instructions is interpreted as follows:

| Eit | 15 | = | 0 | do  | not | issue | CAI |

|-----|----|---|---|-----|-----|-------|-----|

|     |    |   | 1 | iss | sue | CAI   |     |

In all, there are four INOTIFY instructions as follows:

| Name | Bit 15 | 16 | Function           |

|------|--------|----|--------------------|

|      |        |    |                    |

| INEC | 1      | Q  | End + CAI          |

| INEN | ۵      | 0  | End + no CAI       |

| INBC | 1      | 1  | Beginning + CAI    |

| INEN | C      | 1  | Beginning + no CAI |

Figure 9 is a detailed flow chart of the IRTN and INOTIFY instructions.

**Faults**

ه ۲۰۰۰

aults are CFU events which are synchronous with and, in a loose sense, Jaused by software. Eleven fault classes have been defined for the P-400. Several of these classes are further subdivided into distinct types. Of the eleven, three are completely new for the P-400 and, of

PE-T-232

the other eight, three have expanded meaning when in P-400 mode. eleven fault classes and their meanings are:

| Fault      | P-400                                                 | P-300                               |

|------------|-------------------------------------------------------|-------------------------------------|

|            |                                                       |                                     |

| R XM       | Restrict mode violation                               | same                                |

| Process    | Abort flags word .HE. G<br>in PCS on dispatch         | N.A.                                |

| Paçe : ·   | Page Fault (Page not in memory)                       | S 2 M 8                             |

| SVC        | N . A .                                               | Supervisor Call                     |

| UII        | Unimplemented instruction                             | same                                |

| ILL        | Illegal instruction                                   | same                                |

| Access     | Violation of segment<br>access rights                 | Page write violation                |

| Arithmetic | All FLEX + IEX (Integer<br>Exception)                 | FLEX                                |

| Stack      | Stack overflow/underflow                              | Procedure Stack(S-Reg)<br>Underflow |

| Segment    | 1: Segment # tog big                                  | N . A .                             |

|            | <pre>2: Missing segment (SDW<br/>fault bit set)</pre> | N.A.                                |

| Pcinter    | Fault bit in pointer set                              | . N _ A _                           |

The fault handling mechanism consists of two data bases and the CAL instruction. The u-code is in turn divided into a set of 'front-endsfor each fault class and a common fault handler.

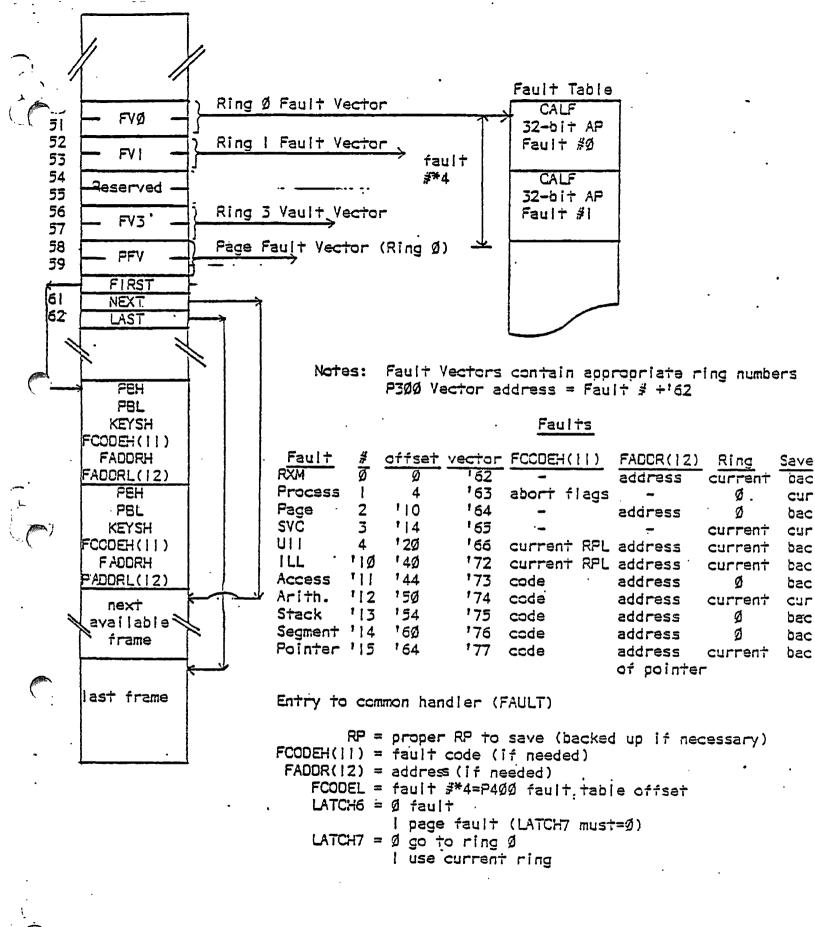

1. Data Bases

The fault data bases consist of the fault vectors and concealed stack in the PCB and the fault tables pointed to by the PCB vectors. Figure 1C shows these data bases as well as the mapping of P-3CO faults to P-400 faults. Also shown in this figure is the differential action taken according to fault class (e.g., what ring to process the fault in) and the set up the u-code "front end" must do before going to the common fault handler.

The underlying philosophy of the four fault vectors is that while some faults may need to be processed by ring 0 code, others may be adequately handled in the current ring of the faulting process. The vectors are in the PCB to allow different processes to have different fault handlers. For example, process A may wish to use a system fault routine to handle pointer faults (dynamic linker) while process 8 may wish to define its own algorithms for resolving pointer faults. Notice that it is always possible for a "current ring" fault handler to call a ring C procedure if the need arises. Note also that page fault has its own vector despite the fact that ring U is entered. For the special case of page fault, only a single, system-wide processor will be use and all FCB page fault vectors will point to the same place.

The concealed stack, also in the FCB, is used to allow fault on fault

onditions. for example, it is quite possible to get a segment fault is processing a segment fault. The only fault which cannot cause ither fault of any type is page fault. Each frame of the concealed stack contains the PE and keys (KEYSH) of the faulting procedure as well as a fault code (to distinguish different types within each class) and a fault address, if appropriate. The stack itself is circular and must have allocated sufficient frames to handle the longest possible sequence of fault on fault that can occur in ring 0. Such a sequence might ce: Pointer (link) fault -> Segment fault -> Stack fault -> Segment fault -> Page fault. Note that this particular sequence occurs before any scitware fault handler is entered. Also, the first segment fault enters ring C, so at least a five-level stack is necessary if the original link fault is to be processed correctly.

The second data base consists of four distinct fault tables, each pointed to by a PCB fault vector. Each entry in the table consists of four words of which the first three must be a CALF instruction. Only the page fault table must be locked to memory and only the ring 0 table (st be in a pre-defined (SOW exists) segment (otherwise, segment fault might recurse infinitely). Naturally, the ring 0 table, as well as the PCP, is carefully audited by ring 0 procedures.

Z. CALF

-

CALF instruction has two major functions. First, to avoid holding if interrupts for too long, the CALF instruction defines a restart int in fault handling since it has a PB (i.e., it is a macro-machine instruction). As a result, it is quite possible to suspend a process in the middle of getting to a software fault handler. Second, it allows a straightforward mechanism to simulate a procedure call from the faulting procedure (at the instruction causing the fault) to the fault handler.

The instruction itself is a three-word generic in which the second and third words are a 32-bit pointer to the fault handler. To simulate the ( acedure call, the PS and KEYS from the concealed stack are placed in the fault handler's stack frame along with the other base registers (only the PE and KEYS have been changed to point to the CALF and to enter 64V addressing mode) to be used by the standard procedure return (PRTN) instruction. In addition, the fault code and address are placed in the fault handler's stack as if they were arguments passed by a standard procedure call (PCL) instruction. After the information is meved from the concealed stack it is popped. In all other respects, CALF is identical to PCL.

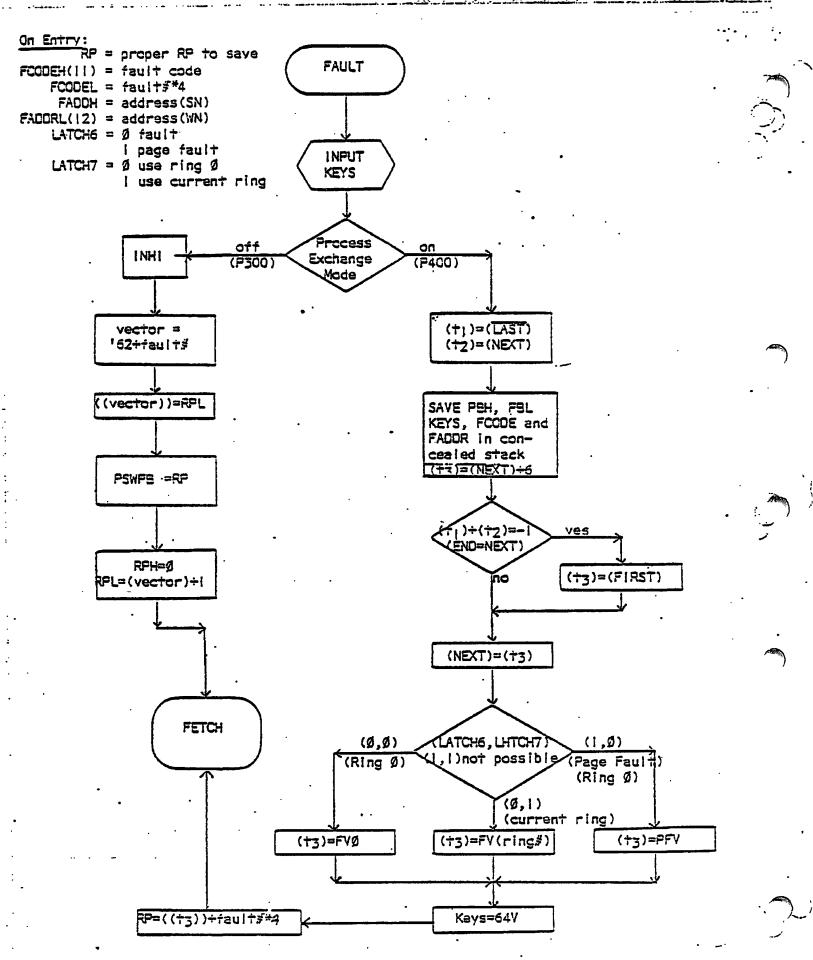

3. Fault Handler

fault hancler is a u-code routine that is entered from the various regult class: 'front ends' and, based on process exchange mode, either imulates a P-3GC type fault (JST\* through segment C fault vectors) or performs the P-4GC fault protocol which includes setting up a concealed stack frame, switching to 64V mode, and determining, on the basis of

PE-T-232

information provided by the 'front end', which fault vector to use andsetting PG to point to the proper CALF in the fault table. Figure 1 is a detailed flow chart of the fault handler and Figure 10 contains a table of the necessary setup performed by each fault class 'front end'. Note that for F-30G faults, the full RP is also saved in the u-code scratca register FSWFB and the machine is inhibited for one instruction if in Ring G.

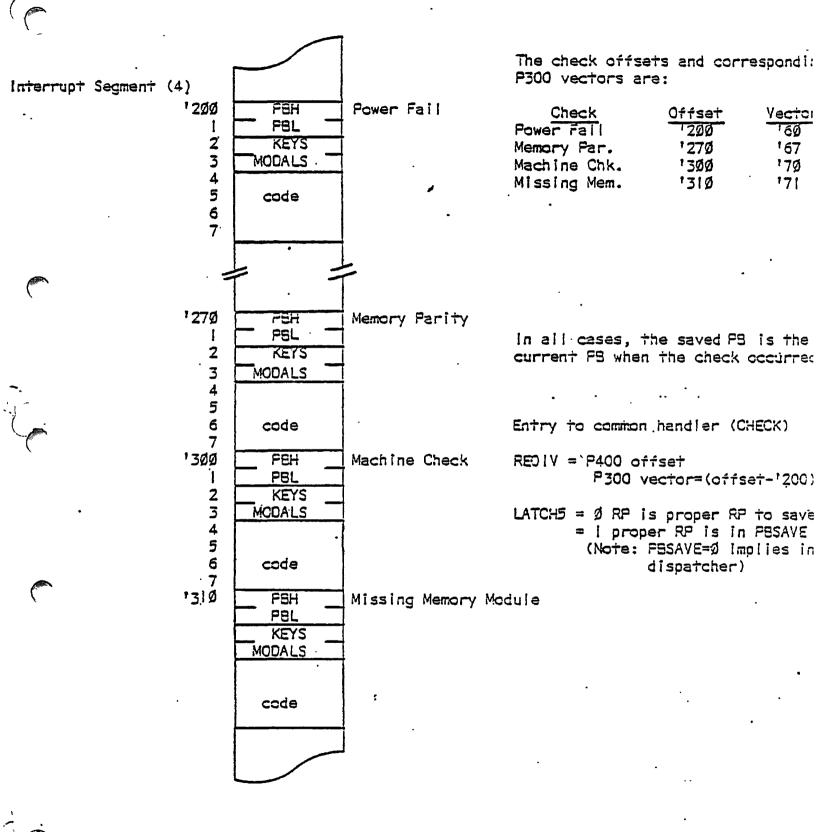

C. Checks

Checks, unlike faults, are CPU events which are asynchronous with, and are not caused by, normal instruction execution. Rather, they are events which are either invisible (e.g., an ECC corrected error) or fatal (e.g., missing memory module) to the currently executing procedure and perhaps the CPU entirely (e.g., machine check). Checks essentially represent processor faults as opposed to process or procedure faults. Four check classes have been defined as follows:

| Check<br>                              | P-400                                           | P-300         |  |  |

|----------------------------------------|-------------------------------------------------|---------------|--|--|

| Power Fail                             | Power Failure                                   | Same .        |  |  |

| Memory Parity .                        | ECC corrected<br>ECC uncorrected                | Memory Parity |  |  |

| Machine Check<br>Missing Memory Module | Fatal CPU error<br>Memory module does not exist | same          |  |  |

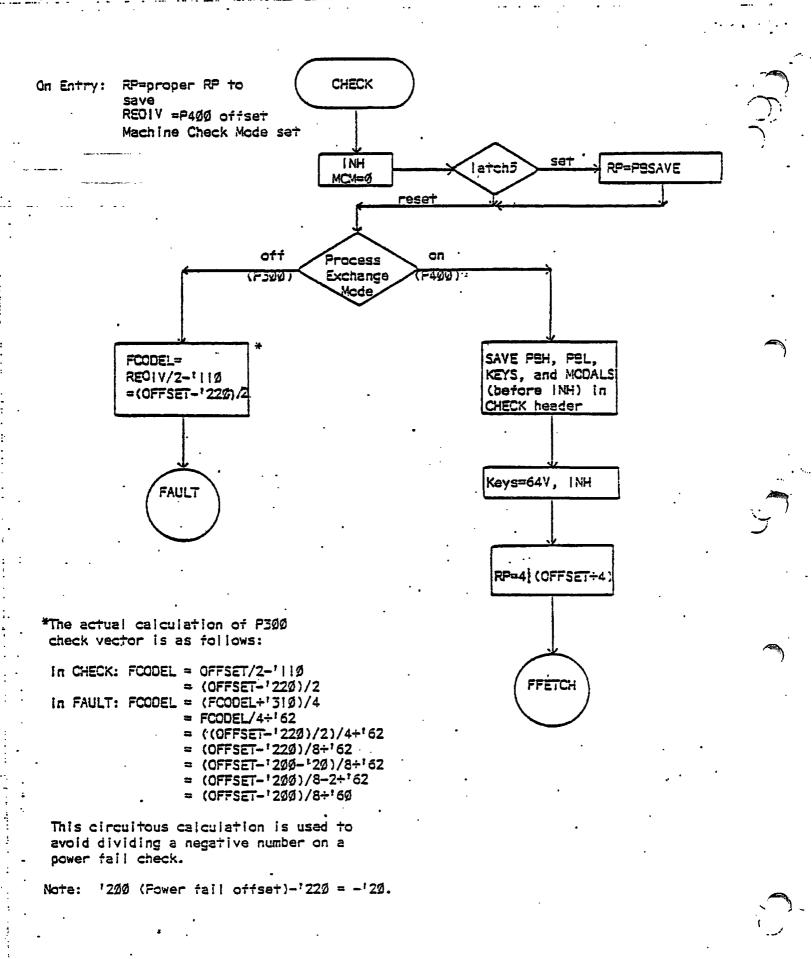

Unlike faults which can be stacked and interrupts which cause a process to be suspended, each check class has a single save area (check block) consisting of eight words in the interrupt segment (#4) in which PB and KEYS (high and low) are saved in the first four locations (check header) and the remaining four locations contain software code (probably a JMP). Figure 12 is a picture of the check data base as well as a description of the necessary u-code setup required before going to the common check handler. In addition to the memory data base, three 32-bit registers are used as a diagnostic status word (DSW) to help a software check handler sort out what happened. Figure 13 shows the format of the DSW.

Check reporting (traps) is controlled by the two low order bits in the modals (KEYSL). The possible modes are:

MCM = 6 no reporting 1 report memory parity (uncorrected) only 2 report unrecovered errors only 3 report all errors

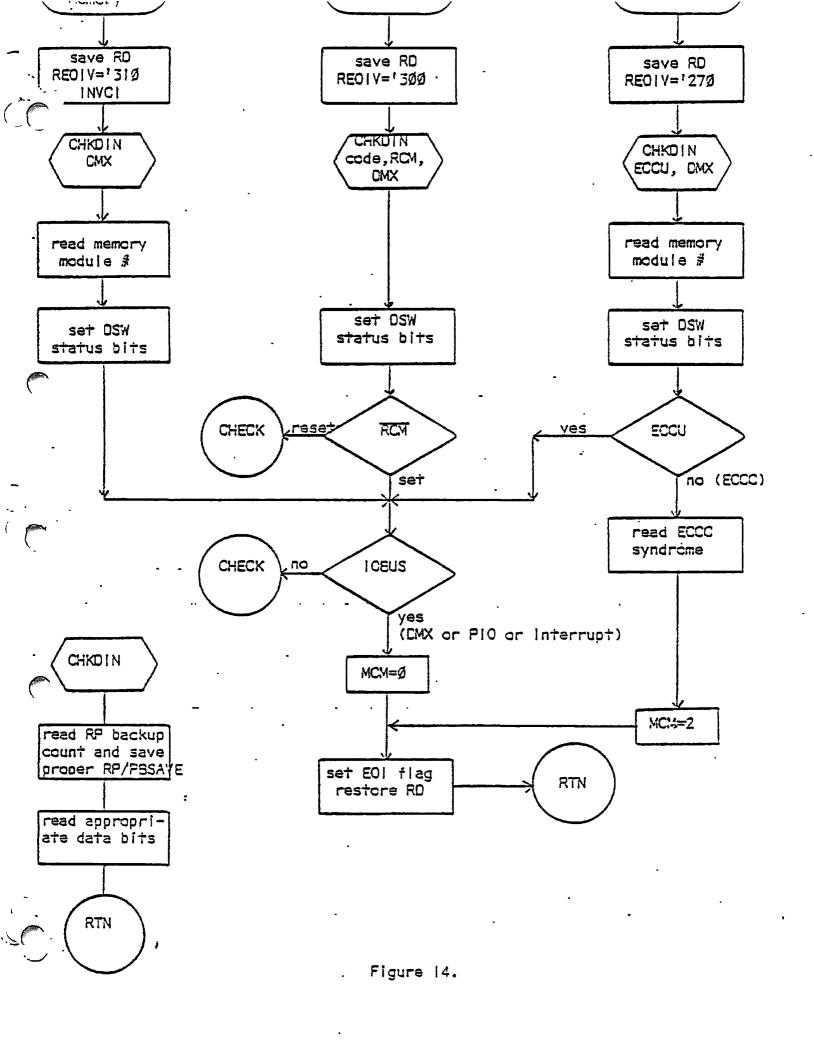

The check trap can result in two possible actions depending upon the type of check that occurred and the type of u-code which was trapped. If the trapped code was either DMX, PIO, or external interrup processing (unless the error was a machine check for RCM parity), or in: the check was for an ECC corrected (ECCC) error, the end-of-instruction flag is set, REOIV is set to the proper

offset/vector, MCM is set to 0 (except ECCC which sets it to 2), and a second RTN to the trapped step is executed. In this way, the IO bus is ays left in a clean state. In all other cases, the check to fitware occurs immediately. Figure 14 is a detailed flow chart showing the operation of the check trap handlers.

The common check handler is entered from various check "front ends" and, based on process exchange mode, either simulates a P-30G type check (JST\* through segment 0 check vectors) or performs the P-400 check protocol which includes setting up the check header, inhibiting the machine, and switching to 64V addressing mode. In either mode, MCM is set to 0 before going to software. Figure 15 is a detailed flow chart of the check handler and Figure 12 contains a table of the necessary setup performed by each check class "front end".

## III. REGISTER FILES

The PRIME 400/500 contains four distinct register files. Each file is further divided into halves, each 32 locations (registers) long, and ch 16 bits wide. One half is referred to as the high half and the other as the low half. Since both halves are addressed together, each register file contains 32, 32-bit register or 64, 16-bit registers. The register files, numbered from G, are used as follows:

RFO - u-code scratch and system registers RF1 - 32 DMA channels RF2 - User register set RF3 - User register set

This layout of register files allows easy expansion to eight register files, thus adding four new user register sets. All user register sets have the same internal format and the DMA register file simply consists of 32 channel registers. Channel register '20 within RF1 is equivalent to the P-300 GMA registers \*20 and \*21. Channel register \*22 is mapped to \*22 and \*23. In this way, the mapping proceeds for each even register in RF1 to channel register \*36, mapped to \*36 and \*37. All geter RF1 registers represent additional DMA channels over the P-300. I gure 1ć shows the internal structure (usage) of RFU and the user register sets (RF2, RF3). Note that all user register sets contain the segment number of the Ready List/PCB segment (OWNERH) and a cell for the modals (KEYSL). It is necessary, before entering process exchange mode, to set GANERH in ALL register sets to the proper value and to NEVER alter it thereafter. Although all register sets contain a cell for the modals, only the current register set (CRS) contains the valid modals. It is therefore recessary, whenever register sets are switched, to copy the modals into the new register set. Currently, only the Dispatcher switches register sets. CRS is defined and specified by the three bit field labeled "CRS" in the modals. Since this field can span up to eight register files, but two are used for ing tode scratch and DMA, user register sets are numbered from 2 - 7. Of Jurse, only 2 and 3 are currently implemented. Thus, for the 400/SGC, the CRS field must always have bit 9 off, bit 10 on, and bit is selects the register set (as if 0 and 1 were the numbers). In fact, the u-code will only look at bit 11.

Direct register file addressing (not using CRS) is accomplished eitherwith the LOLR/STLR instructions or via the control panel. The Registe Files are ordered sequentially with an absolute address of 0 addressing RFG-register 0 (u-code scratch/system file), 140 addressing RF1-register 0 (DMA file), 110C addressing RF2-register 0 (user set 2), and 1140 addressing RF3-register 0 (user set 3).

Beside each register name, where appropriate, is, the PRIME-300 mode meching from address tracs to registers (e.g., the X register is the high half of GR7).

### IV. CONTROL PANEL

The control panel for the P-4CC/SGG is the same physical panel used for the P-1GG/2GG/3GG. It's functionality was enhanced by improving the u-code in the CP. All switches and selectors operate exactly as for the P-3GC with the exception of the sense switches in the up position. Figure 17 is a diagram of the functionality of the switches. Notice that with all switches down, any FETCH/STORE operations are to/from memory-macoed. As long as segmentation mode is not turned on, mapped and absolute are the same, thus preserving compatibility. If SS4 down were absolute, address traps could not occur and would thus be incompatible. Notice also that SS5-16 in the up position changes meaning depending upon SS4. When-mapped, all 12 switches are read as a 12-bit segment number. When absolute, SS11-16 are used as the 6 high order bits of the 22-bit physical address. To address any P-307 registers, all sense switches should be placed in the down position and accresses between C and '37 specified.

P-400/SCC registers are accessed by raising SS1. Then, if SS2 is down, the low order 5 bits of the address are used to access 32-bit registers C-137 within CRS. If SS2 is faised, the full 7 bit address is used to access any register in any register file. The addresses, as shown in Figure 16, are U-137=u-code scratch/system, 140-177=DMA, 100-1137=User set 2, and 1140-1177=User set 3. SS4 is used to access either the high half (up) or the low helf (cown) of the selected register. For all register accesses, the Y+1 functions will advance the register address before the access, exactly as for memory accesses. Wrap around will occur on the appropriate number of bits, since any bits of higher order are ignored for the access.

The control panel data register is TR2H and the address register is TR3. Upon entering the control panel routine, RP is saved in TR3 and (RF) is saved in TR2H. In addition, the keys (XEYSH) are updated to reflect accurately the live keys. Thereafter, TR3H is not altered by the control panel itself so RPH is always remembered. However, on exit, PEH is used to update RPH and KEYS is used to update all the keys. As a result, single stepping can change segments as well as keys and modals. Figure 18 is a detailed flow chart of the control panel routine.

The only exception to the control panel entry protocol is that if af Fault, Check, or external Interrupt attempts to vector through a vector containing 0 in P-300 pode, the following registers will contain:

- - -

ا این از میرونیسیست در با در مانه در این است. از میرونیسیست از این وس

RP: address of 'trapped' instruction PBH: SN of 'trapped' instruction KEYSH: proper keys TR2H: (data) 0 TR3: (address) G[0 TR2L: address, in segment 0, of the 'vector' containing 0

## V. CP TIMER

Resolution = 1024 u-sec

Turned on by DISPATCHER before dispatch.

Turned off by: WAIT after/during save DISP before changing CRS

On tick, u-code increments the interval timer (TIMER) in RF(CRS). When that overflows, bit 16 in the PCE abort flags (memory) is set to cause a process fault.

It is the responsibility of software that resets the interval timer to maintain the elapsed timer.

Ready List: All pointers are 16-bit word number pointers within the FC3 segment. The segment number is contained in the high portion of the CWNER pointer within each register set.

All PCB start addresses must be even (bit 16 =  $\emptyset$ ). The end of the ready list is marked with a EQL entry = 1.

FIGURE 1.

ر گر

Process Control Block (PCB)

0-254567 evel link WLSN (Ø=on ready list) WLWN FIRE ADOC Reserved Elapsed Timer - DTARZ **DTAR3** INTERVAL LIMER (LIVE) Save mask KAVE GRØ . GRI -· GRZ GR3 GR4 GR5 GR6 order fixed, locations flexible depending upon GR7 save mask FFØ F71, PS · **S**8 LB XB FVØ FYI Reserved FV3 -. PFV --·· • CONCERIED STECK FIRSI CONCERIED STRCK NEXI LAST Concealed Fault Stack (6 words/entry)

Figure 3.

. . .

.

• • •,

Finne 8

Figure 10.

• \* • • • • • • •

•

Software check catchers reside in the interrupt segment (4) and are 8 words each. The first 4 words are used as a PSW save area as:

| Diagnostic                                                                                                                                               | c Status Word (DSW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ······································ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Bits],<br>33,<br>49,                                                                                                                                     | Registers '34,1355'36 (named DSWRMA, DSWSTAT, and DSWP9)<br>,32: DSWRMA<br>,48: DSWSTATH Valid on all checks except Power Fail<br>,64: DSWSTATL as follows:<br>,80: DSWF9                                                                                                                                                                                                                                                                                                                                                                                      |                                        |

|                                                                                                                                                          | 1     2     3     4     5     6     7     .8     9     10     11     12     13     14     15     16       33     34     35     36     37     38     39     40     41     42     43     44     45     46     47     48                                                                                                                                                                                                                                                                                                                                          | DSWSTATH                               |

|                                                                                                                                                          | C     M     M     M     Machine     R     E     E     Eup     RP     Eackup     D     10       I     C     P     M     Check     Code     C     C     C     Inv     Count     M     Eus       M     C     C     U     C     U     C     X     X                                                                                                                                                                                                                                                                                                                | • • •                                  |

|                                                                                                                                                          | 1       2       3       4       5       6       7       8       9       10       11       12       13       14       15       16         17       18       19       20       21       22       23       24       25       25       27       28       29       30       31       32         49       50       51       52       53       54       55       56       57.       58       59       60       61       62       63       64                                                                                                                          | DSWSTATL                               |

|                                                                                                                                                          | RMARes ECC Syndrome Mod Reserved u-Verify test \$<br>prv-<br>inved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                      |

| 34: MC:<br>35: MP<br>36: MM<br>37,39: Mac<br>9=f<br>2=4<br>3=0<br>4=f<br>5=f                                                                             | -Check Immediate<br>-Machine Check<br>-Memory Parity (ECC)<br>=Missing Memory<br>chine Check Code<br>Peripheral Data (EPD) Output<br>Peripheral Address (EPA) Input<br>Memory Data (ECD)<br>Peripheral Address (EPA) Output<br>RDX-EPD Input<br>Memory Address (EMA)                                                                                                                                                                                                                                                                                           | ·<br>J                                 |

| 7=6<br>40: Not<br>41: ECC<br>42: ECC<br>43: Bup<br>44,46: RP<br>47: CMD<br>48: IO<br>48: IO<br>49: FMJ<br>50: Res<br>51,55: ECC<br>56: Mod<br>57,58: Res | Register File<br>+ RCM Parity (Reset for RCM Parity error - XCS only)<br>CU=ECC Uncorrectable Error<br>p Inv=RP backup count (44-46) Invalid<br>Eackup Count-emount RPL (DSWPS) was incremented in current instru<br>X, set if check occurred during EMX<br>Eus, set if check occurred during EMX<br>Eus, set if check occurred during EMX, PiO or Interrupt u-code<br>WA Inv=DSWRMA Invalid (Possible from ECCU and MM only)<br>pserved<br>CC Syndrome=5 syndrome bits on a corrected error<br>od \$=bow order address bit of memory module causing the error | · · · · ·                              |

| Validity:<br>Alwa<br>If b<br>If b<br>It is the                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                                                                           |                                                      |                                                    | 1144                                                                     | •                                            | <u></u>                                                                                                                             | <u>п.ч.</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | LCW                                             | 1 4002                                                                                                                                                        | ~ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Q IRRIZINA 506 TREMXZ<br>IRRIZ IRR 506 TREMXZ<br>IRRIZ REMXZ<br>IRRIZ REMXZ | PCEA<br>PCEB                                           | 0 - 2 3 4 5 6 7 0 - 2 5 4 5 6 7 0 - 2 5 4 5 6 7 0 - 2 5 4 5 6 7 0 - 2 5 2 2 2 2 2 5 5 5 5 5 5 5 5 5 5 5 5 | (2Ø)<br>(22)<br>(24)<br>(25)<br>(32)<br>(32)<br>(34) | <pre>(21) (23) (25) (27) (31) (33) (35) (37)</pre> | 401423445670123345567012345670123456777777777777777777777777777777777777 | •                                            | 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 7 0 1 2 2 2 2 2 2 2 2 5 3 3 3 3 5 5 7 | GRØ<br>GR1<br>GR2(1,A,LH)<br>GR3(EH)<br>GR4<br>GR5(3,S,Y)<br>GR6<br>GR7(Ø,X)<br>FRØ(13)<br>-<br>FR1(4)<br>-(6)<br>FB<br>SB(14)<br>LB(16)<br>X8<br>DTAR3(1Ø)<br>DTAR2<br>DTAR1<br>DTAR2<br>DTAR1<br>DTAR2<br>CTAR1<br>DTAR9<br>KEYS<br>OWNER<br>FCCDE(11)<br>FACCR<br>TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                               | 100<br>101<br>102<br>103<br>104<br>105<br>106<br>107<br>110<br>112<br>113<br>115<br>117<br>120<br>122<br>125<br>125<br>132<br>134<br>135<br>135<br>135<br>135 |   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Adr FIS<br>Mode EX<br>EX<br>E<br>S<br>S<br>R<br>R<br>I |                                                                                                           | 1216 418                                             | S                                                  |                                                                          | ENB:<br>VIM:<br>CRS:<br>MIO:<br>PXM:<br>SEG: | Set=en<br>Set=ve<br>Curren<br>Set=Pr<br>Set=Pr<br>Set=Set                                                                           | SL (Modals)<br>17 8 9 1 CH 12<br>CRS M<br>CRS M<br>C | x E<br>M G<br>rupt mode<br>et<br>ge Mode<br>cde |                                                                                                                                                               |   |

•

•

1 Dispatcher Jave Done 🕠

•

Figura 16.

٠

•

•

| icwn  | memory   | up   |          |     | absolute  |   | Fhysical Address 95<br>Segment \$ | -90 |

|-------|----------|------|----------|-----|-----------|---|-----------------------------------|-----|

| άμ    |          | down | CRS      |     | low half  |   |                                   |     |

| up re | regişter | up   | absolute | •   | high half |   | SS11-16                           |     |

|       | S\$1     |      |          | SS3 | SS4       | / |                                   | À.  |

Notes: With all switches down, control panel works exactly as for the P-300 following either a Master Clear or a HALT if not running in segmented mode. It is necessary to make mapped memory accesses if address traps are to be generated. If running segmented, memory accesses will be mapped to segment 0 unless an explicit segment number is entered in SS5-16.

> Registers: Register address is in address register (switches down) For CRS, only low order 5 bits are used; for absolute, only low order 8 bits are used Y+1 (STORE/FETCH) operates exactly as for memory with the address being pre-incremented.

Null Vector: In P-300 mode, if an external interrupt, fault, or check attempts to vector through a memory location containing a 0, the following action is taken:

> HALT data <u>and</u> address lights cleared RP = address trapped PBH = RPH TR2L = address of vector

Figure 17.